### **TECHNOLOGIES of INTERCONNECTIONS in ELECTRONICS**

**Industry-wide Student Challenges**

#### Organized by:

### National University of Science and Technology POLITEHNICA Bucharest, Romania

http://www.upb.ro

Faculty of Electronics, Telecommunications and Information Technology

https://etti.upb.ro/

Faculty of Mechanical Engineering and Mechatronics

http://www.mecanica.pub.ro

Transilvania University of Brasov Transilvania University of Braşov, Romania

https://www.unitbv.ro/en/

Faculty of Electrical Engineering and Computer Science

https://iesc.unitbv.ro/en/

**Technical University of Cluj-Napoca**

https://www.utcluj.ro/en/

Faculty of Electronics, Telecommunications and Information Technology

https://etti.utcluj.ro

Association for Promoting Electronics Technology APTE, IMAPS Chapter Romania

http://www.apte.org.ro

Regional Development Agency ADR Centru

https://www.adrcentru.ro/

Center for Technological Electronics and Interconnection Techniques

http://www.cetti.ro

#### and supported by:

EPETRUN (Electronics Packaging Education Training and Research University Network)

EDITORS: Paul Svasta, Cosmin Moisa, Cătălina Neghină, Delia Lepădatu

DTP: Bogdan Mihăilescu Publisher: Tiporex Alba Iulia

# TECHNOLOGIES OF INTERCONNECTIONS IN ELECTRONICS

INDUSTRY-WIDE STUDENT CHALLENGES

34<sup>th</sup> Edition

Transilvania University of Braşov, April, 02 – 05, 2025

## TECHNOLOGIES OF INTERCONNECTIONS IN ELECTRONICS – 2025 INDUSTRY-WIDE STUDENT CHALLENGES

#### **Program Brochure**

| weicome to the 2025 Event                                                      | ⊥   |

|--------------------------------------------------------------------------------|-----|

| Event Committees 2025                                                          | 17  |

| TIE 2025 Event Agenda                                                          | 20  |

| TIE & TIE <sub>M</sub> & TIE <sub>PLUS</sub> past, present and future editions | 27  |

| Workshop Program                                                               | 29  |

| Workshop ADR Centru (EEN)                                                      | 31  |

| Wednesday, April 2 Program                                                     | 37  |

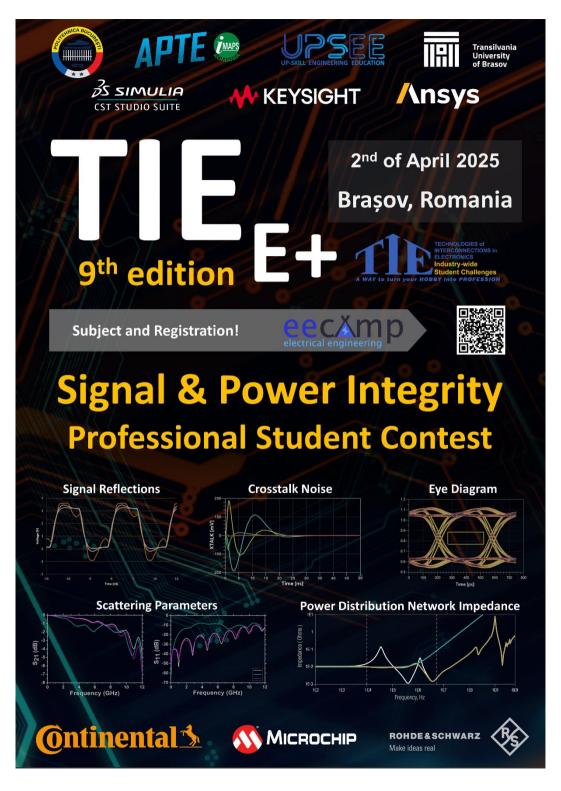

| TIE <sub>Eplus</sub> Contest                                                   | 39  |

| Thursday, April 3 TIE <sub>MPLUS</sub> , TIE <sub>TPLUS</sub> , TIEμ Program   | 44  |

| TIE <sub>MPLUS</sub> Contest                                                   | 45  |

| TIE <sub>TPLUS</sub> Contest                                                   | 49  |

| TIEμ Contest                                                                   | 53  |

| Thursday, April 3 MICROELECTRONICS DAYS Program                                | 58  |

| Dr. Christian VON ALBRICHSFELD                                                 | 60  |

| Addressing semiconductor talent gap: research on industry                      |     |

| skills needs, Victoria CUMMINGS                                                | 61  |

| Introduction to Package Design and Analysis, Carolyn TUBILLO                   | 62  |

| Friday, April 4 MICROELECTRONICS DAYS Program                                  | 63  |

| European Chips Skills Academy, Victoria CUMMINGS                               | 65  |

| Silicon-to-Systems: Path towards Next Generation Design,                       |     |

| Dr. Peter TRANITZ                                                              | 66  |

| Friday, April 4 TIE <sub>E</sub> , TIE <sub>M</sub> Program                    | 67  |

| TIE <sub>E</sub> Contest                                                       | 69  |

| TIE Certificate for recognition by the industry of students                    |     |

| competence in PCB design                                                       | 73  |

| TIE <sub>E</sub> Committees                                                    | 74  |

| TIE E Winners                                                                  | 76  |

| TIE <sub>E</sub> 2025 Participants                                             | 78  |

| TIE <sub>M</sub> Contest                                                       | 89  |

| TIE <sub>M</sub> Committees                                                    | 93  |

| TIE <sub>M</sub> Participants                                                  | 94  |

| Industry                                                                       | 99  |

| Research                                                                       | 111 |

| WELCOMES TO TIE 2026                                                           | 116 |

#### **Dear Participants of TIE 2025,**

We warmly welcome all the TIE participants to this event, which is dedicated to training, evaluating and validating future professionals in the field of electronic packaging.

TIE provides a platform where students are challenged to address real-world issues in the electronics industry, specifically in electronic packaging, a crucial aspect of the design and production of electronic products. In this context, the collaboration between academia, responsible for educating and training future engineers, and industry, the direct beneficiary of these graduates, forms a high-performance ecosystem. This partnership ensures mutual benefits: students gain access to highly qualified jobs, the industry recruits well-trained engineers, and academic staff can effectively tailor curricula to meet the evolving needs of the sector.

The challenges presented at TIE 2025 consist of six topics, developed by industry professionals in collaboration with academic experts, for students to solve. These topics reflect various challenges encountered in electronic product design.

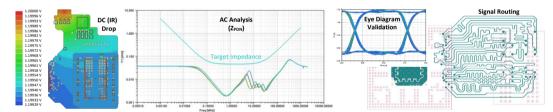

The current edition focuses on three electrical topics: designing a medium-complexity PCB, evaluating the signal integrity and power behavior of an interconnection structure, and designing the interconnection within a System-in-Package (SiP). Additionally, three non-electrical topics cover optimizing the mechanical design of an electronic product, assessing its response to mechanical stress, shocks, and vibrations, and evaluating its thermal behavior and management. The challenges are supported by industry-leading software solutions, including advanced tools for mechanical design and thermal analysis. These software solutions enable students to simulate and optimize their designs with high accuracy, enhancing their learning experience.

The complexity and success of TIE would not have reached its current level without the significant involvement of all participants, industry professionals, academic staff, and, most importantly, the enthusiastic students who seize this opportunity to demonstrate their skills and creativity.

We also extend our gratitude to the companies that have provided essential modeling and simulation licenses. Specially, we would like to acknowledge **Cadence** offering over 30 licenses for TIE micro, made available to the organizers for an entire year, along with the necessary technical support. This generous contribution has been a key factor in the success of TIE 2025.

#### Welcomes to TIE 2025 Event

A special thank you goes to all the volunteers—over 70 of them—who have dedicated their time and effort to ensuring the best organizational and technical conditions for the event. We also deeply appreciate the support of our sponsors, whose financial contributions have made it possible to host TIE 2025 under excellent conditions.

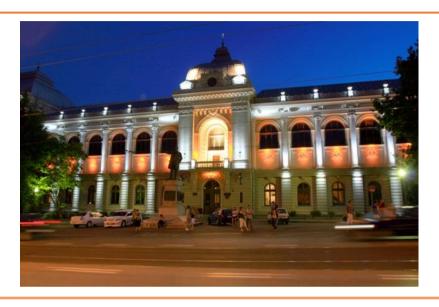

Finally, we must highlight the invaluable involvement of **Transilvania University of Braşov** and the **Regional Development Agency Centru** in creating the welcoming and family-like atmosphere that defines TIE. This event has truly become the **spring convention of the electronic packaging community** in this part of Europe.

We wish all participants a pleasant and productive stay in Braşov, Romania!

Prof. D.H.C. mult. Paul SVASTA, Ph.D.

National University of Science and Technology

POLITEHNICA of Bucharest, Romania

APTE-Association for Promoting Electronics Technology

TIE General Chair

**Prof. Ovidiu POP, Ph.D.**Technical University of Cluj-Napoca

TIE General Co-Chair

#### Dear participants and guests,

On behalf of the local organizing committee, we are delighted to welcome you to Braşov for the 2025 edition of the Technologies of Interconnection in Electronics (TIE) event. By organizing Romania's first Microelectronics Day, Transilvania University of Braşov highlights its commitment to current technological advancements and its vision for the future, with microelectronics playing a key role.

Building on the region's rich scientific, industrial, and cultural traditions, Transilvania University of Brașov has a longstanding history of participating in TIE events, while local industrial partners continue to expand their presence in electronics, digital design, and verification.

Returning to Braşov after more than a decade, the event has expanded to 6 student challenges covering different aspects of electronic packaging:  $34^{th}$  edition of the classic PCB design challenge TIE<sub>E</sub>, the  $4^{th}$  edition of TIE<sub>M</sub> for mechanical design, the  $9^{th}$  edition of the advanced analysis TIE<sub>EPLUS</sub>, the  $3^{rd}$  edition of TIE<sub>MPLUS</sub>, the  $3^{rd}$  edition of for TIE<sub>TPLUS</sub> (thermal) and second edition for TIE $\mu$  (micro).

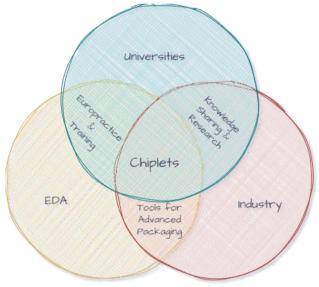

TIE is an established student challenge, a proven path for students to get hands-on experience with hot industry topics such as chiplets and advanced packaging. Furthermore, students get access to state-of-the-art EDA tools, trainings and documentation.

We are looking forward to meeting you in Brasov for a great TIE 2025!

#### Prof. Titus Constantin BĂLAN, Ph.D.

Dean of the Faculty of Electrical Engineering and Computer Science

Transilvania University of Brasov

Transilvania University of Brașov TIE 2025 Chair

Coordinator of the Smart Electronic Systems Research Center Transilvania University of Braşov TIE 2025 Co-Chair

#### TIE – a Best Practices for the Romanian Universities Contribution to Microelectronics Value Chain in Europe

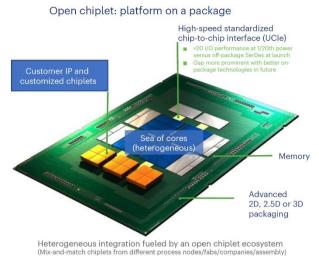

Modern life heavily relies on mobility, communication, smart environments for living and working, and gadgets for entertainment and health. Smart devices can enhance our senses, understand and anticipate our needs, communicate securely, and act quickly and safely. Their evolution towards greater intelligence is unstoppable. All these devices are powered by semiconductors, which integrate an increasing number of transistors, now approaching atomic dimensions.

The global semiconductor market surpassed \$550 billion in 20231. Europe accounts for less than 10% of this market2. In 2023, the Council of the European Union approved the Chips Act, aiming to invest €43 billion to double Europe's share of global semiconductor production to 20% by 2030. The current geopolitical situation highlights the need for Europe to build its own defense system, which relies on semiconductor sovereignty.

We are facing a significant technology gap between Europe, Asia, and America. In my opinion, the biggest challenge we must address at both the European and national levels is developing a qualified workforce capable of developing the microelectronics value chain. The United States began reducing its semiconductor manufacturing footprint when DRAM production was transferred to Japan. Later, TSMC (Taiwan Semiconductor Manufacturing Company) emerged, gradually taking over and advancing the most sophisticated semiconductor technologies3. The United States and Europe retained only the design of increasingly complex devices, design tools, and EUV lithography machinery. Now, it is time to work diligently to close this gap.

In Romania, in the early '90s, all investment in microelectronics was halted, and university programs underwent continuous restructuring of their curricula. However, in Romanian universities, there were faculty collectives that continued to maintain relevant curricula for the microelectronics value chain and elevate the scientific and technological standards. They leveraged opportunities such as educational exchanges, European grants, and industry research projects to build laboratories and conduct significant research. The results of these efforts were utilized to improve and upgrade courses.

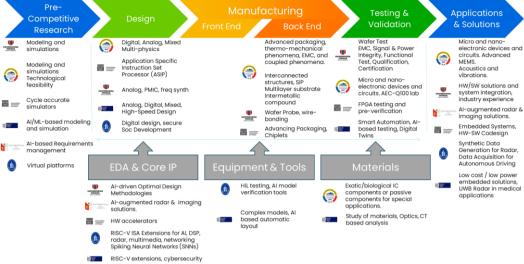

Based on my personal research, made possible through NXP Semiconductors Romania's participation in IPCEI ME/CT (https://ipcei-me-ct.eu/), in collaboration with six universities in Romania4, I identified the mapping of competencies presented in Figure 1

<sup>&</sup>lt;sup>1</sup> Source: https://investors.nxp.com/static-files/8e7721d4-bf71-493b-b4d6-e179214de061

<sup>&</sup>lt;sup>2</sup> Source: https://www.eusemiconductors.eu/sites/default/files/ESIA WSTS PR 2212.pdf

<sup>&</sup>lt;sup>3</sup> Taiwan began ramping up skills in microelectronics in 70s. More details here: https://en.wikipedia.org/wiki/Semiconductor industry in Taiwan

In IPCEI ME/CT, NXP Semiconductors Romania collaborates with the following universities: Universitatea de Știință și Tehnologie Politehnica București (UPB), Universitatea Politehnica Timișoara (UPT), Universitatea Tehnică din Cluj Napoca (UTCN). Universitatea Tehnică Gheorghe Asachi din Iași (UTIS), Universitatea Transilvania din Brașov (UTBV), Universitatea din Craiova (UCV). Only them are reflected in Figure 1

## Romanian Universities Contributions to Microelectronics (ME) Value Chain PreCompatitive Design Manufacturing Testing & Applications Applications

Figure 1. Mapping of Competencies for Microelectronics Value Chain in Romanian Universities

Besides the universities reflected in this figure, it is worth to mention that Universitatea Lucian Blaga din Sibiu, Universitatea "Ștefan cel Mare" din Suceava, Universitatea "Dunărea de Jos" din Galați also maintain and train important competencies for the Microelectronics Value Chain.

These universities collaborate with the industry to organize the annual TIE (Technologies of Interconnection in Electronics) student contest, which has been running for over 30 years and is likely the longest and most important electronics contest in Europe. Participants are challenged to learn, experiment, and achieve results in six areas of electronics interconnections: PCB design (TIE $_{\rm E}$ ), signal and power integrity (TIE $_{\rm EPLUS}$ ), mechanical design of electronic packages (TIE $_{\rm M}$ ), structural and thermal management analysis (TIE $_{\rm MPLUS}$ ), thermal management optimization (TIE $_{\rm TPLUS}$ ), and system-in-package design (TIE $_{\rm M}$ ). So far, more than 3,000 students have participated, with over 1,500 successfully completing the competition and receiving industry-certified diplomas.

Romania is one of the largest countries in Europe. We have strong universities with over 10,000 students in electronics and more than 13,000 students in computer science, along with significant research capabilities. Major semiconductor companies such as NXP Semiconductors, Infineon, Microchip, Continental, and Bosch are present in Romania. We have

the potential to expand the microelectronics industry in Romania, offering growth opportunities for companies and making a substantial impact on developing Europe's sovereignty in semiconductors and related industries.

#### Radu PREDA,

Manager of Partnerships under Subsidy Projects, NXP Semiconductors Romania

#### **Welcomes to TIE 2025 Event**

#### **TIE 2025**

What is TIE today? Today TIE is more than just an academic competition, it is the platform that brings together industry and academia to create the premises, the opportunity to share, to experience the real challenges that new technologies bring to this hyperdynamic field.

The close collaboration between academia and industry offers future engineers the opportunity to improve, evaluate and validate the theoretical and applied aspects acquired during their university studies as well as those specific to the engineering profession.

Each stage of the competition is an opportunity to learn, develop skills and gain valuable feedback, highlighting its role as a link between academic knowledge and its practical application in the professional field.

The permanent technological progress of the companies involved in research, design, development of both CAD/EDA concepts and top of the range products has required TIE to reinvent itself year after year, to reorganize itself.

Today, TIE is a mature platform that brings together both electrical/electronic (TIE $_{\rm E}$ , TIE $_{\rm EPLUS}$ , TIE $_{\rm H}$ ) and non-electrical (TIE $_{\rm M}$ , TIE $_{\rm MPLUS}$ , TIE $_{\rm TPLUS}$ ) aspects, covering the whole multidisciplinary spectrum of processes.

The TIE community acts as an engine for science, technology, advanced manufacturing, promotes the development of education.

I am pleased to note that the fruitful, sometimes contradictory, discussions during the sessions organized under the auspices of the TIE have led to profound changes, in terms of subject descriptions, teaching portfolios and even the development of new training methods in which the applied learning component is a priority.

Moreover, I observe that this impactful, hyper-competitive field such as electronic systems development and applications is pushing to the maximum the massive integration of available design resources such that the design constraints, robustness, reliability, cost and technological limitations encountered not so long ago have been successfully overcome.

#### **Welcomes to TIE 2025 Event**

The course of this scientific event leads me to believe that in future TIE editions we will also find competition sessions dedicated to processor design, parallel design, concurrent integration, etc.

Finally, I would like to express my thanks to all those involved in the organization of the current edition of TIE, sponsors and exhibitors, whose contribution has been essential to maintain a high level of quality.

**Lecturer Marius CARP, Ph.D.**Transilvania University of Braşov  $TIE_E$  Technical Committee – Academic Trainer

#### Preface TIEM

The student contest named Technologies of Interconnections in Electronics, Mechanical concept (TIE<sub>M</sub>) involved a great number of participants, graduated students, in the last five years. It is a big challenge and an opportunity to evaluate the knowledge acquired during four years of study and moreover the passion of participants for computer aided design in this interdisciplinary field implying mechatronics and electronics. It is a contest where the mechatronics students are working near their colleagues studying electronics. As we know, the Electronics Packaging, the Design for the Future, has been one of the most important research activities in our university since 2019 implying teachers, researchers as well as students and young engineers.

Since the beginning it was a great success due to the company's involvement, such as Continental Timişoara, Continental Sibiu that are interested in testing and pointing out the solutions discovered by the students, when some practice problems should be solved. The requirements are testing, refrigeration and thermal evolution during functioning, manufacturing and applying the design principles for all of these. The teams are evaluated by the experienced engineers working in the company and by the teachers, other than from the university the students come from. Finally, only the best students are rewarded, but all of them have achieved a new step, their satisfaction with finding out a passion, which could be for long time and could be in continuous evolution, so it is a great success for them, for teachers and for the contest committee.

We aim to improve this activity and to turn it into a hobby for the students and young engineers, following the idea of competition approved by companies and universities.

**Lecturer Alina SPÂNU, Ph.D.**POLITEHNICA Bucharest

TIE<sub>M</sub> Technical Committee – Academic Trainer

#### TIEM, TIEMPLUS, and TIETPLUS competitions

The TIE<sub>M</sub>, TIE<sub>MPLUS</sub>, and TIE<sub>TPLUS</sub> competitions play a critical role in uniting academic and industrial partners by offering a realistic simulation of the challenges encountered in the design, development, and validation of electronic modules. These events serve not only as a testing ground for theoretical knowledge but also as a platform where practical skills and innovative solutions are developed and refined.

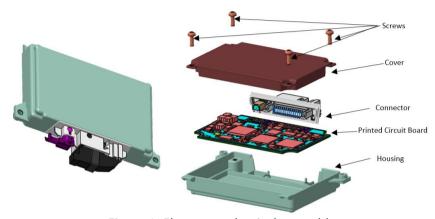

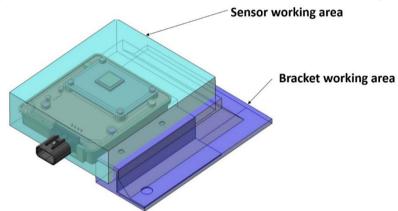

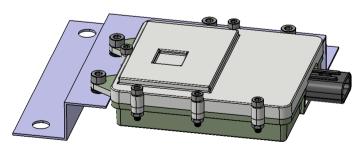

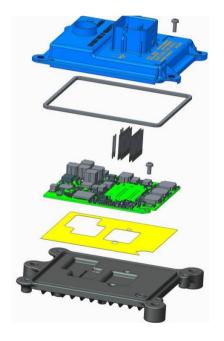

In the  $TIE_M$  contest, participants are tasked with developing a robust mechanical design for electronic modules within a constrained four-hour timeframe. This aspect of the competition mirrors the time-sensitive decision-making process found in professional environments and underscores the importance of efficient problem-solving and rigorous design methodology. It provides students with firsthand experience in applying classroom concepts to real-world scenarios, while simultaneously offering industry professionals a glimpse into the emerging talent and novel approaches that could shape future advancements.

The advanced simulation challenges,  $TIE_{MPLUS}$  and  $TIE_{TPLUS}$ , further enhance the educational and practical value of the contests by introducing structural analysis and thermal management into the equation. These simulations are crucial for validating design integrity and ensuring product reliability under operational stresses. The extended preparation period, supplemented by expert-led workshops, allows participants to delve deeply into the mechanics of material behavior and thermal dynamics. For academic institutions, these exercises integrate computational methods with traditional engineering education, while for industrial partners, they reflect the rigorous procedures essential for product quality assurance.

Overall, the structured approach of these competitions provides a comprehensive overview of the developmental challenges associated with electronic module design and validation. The process emphasizes the significance of interdisciplinary collaboration, iterative improvement, and early error detection, all of which are vital to successful

product development. By bridging the gap between theoretical instruction and practical application, the TIE series of events not only cultivates a more capable future workforce but also fosters a productive dialogue between academia and industry, ultimately driving innovation and ensuring that modern engineering practices meet the evolving demands of the market.

# Philip COANDĂ, Ph.D. Continental Automotive Timişoara TIE<sub>TPLUS</sub> Co-Chair, TIE<sub>MPLUS</sub> Committees

### TIE<sub>TPLUS</sub> Contest: Academic Growth and Real-World Skills in Thermodynamic Simulation

The TIE<sub>TPLUS</sub> contest is a unique opportunity for students passionate about electronic engineering and thermal simulation of electronic equipment. It focuses on using computer-aided thermodynamic simulations (CAE) to analyze and improve the thermal performance of electronic systems. By applying advanced numerical methods, participants not only sharpen essential technical skills but also prepare themselves for the challenges of today's technology-driven industries.

#### Why Thermodynamic CAE Simulations Matter

In modern engineering, thermodynamic Computer-Aided Engineering (CAE) simulations are a key tool for designing and optimizing technical components. They allow engineers to examine temperature distribution and heat flow in detail, helping to predict how heat will affect the performance and reliability of electronic equipment. Using methods such as Finite Element Analysis (FEA) and the Finite Volume Method (FVM), engineers can tackle real-world challenges in industries like electronics, automotive, aerospace and energy, where effective thermal management is critical.

As part of the  $TIE_{TPLUS}$  contest, students are tasked with running an advanced thermodynamic CAE simulation of an electronic product. They explore both natural convection and forced conduction scenarios, giving them hands-on experience with fundamental thermal management principles. This directly helps prevent overheating and improves the efficiency and reliability of electronic systems.

#### Real Benefits for Students and Future Career

$TIE_{TPLUS}$  is more than just a competition — it's a platform for personal and professional growth. Students put their theoretical knowledge to the test while gaining valuable practical experience with modern CAE software widely used in industry. Beyond technical skills, the contest strengthens problem-solving abilities, critical thinking, and analytical reasoning — qualities highly sought after by employers.

One of the key components of the contest is writing a detailed technical report based on the simulations. This not only deepens your understanding of thermodynamic phenomena but also improves the ability to communicate technical findings clearly and effectively — a crucial skill for any engineering career.

#### **Bridging Academia and Industry**

What makes TIE<sub>TPLUS</sub> stand out is its strong connection to the professional world, especially through its collaboration with Continental, a leading global company. This partnership helps bridge the gap between university and industry. Students gain insight into real industrial challenges, while companies benefit from fresh perspectives and well-prepared future engineers.

TIE<sub>TPLUS</sub> is an excellent opportunity to combine academic knowledge with real-world applications, opening doors to successful careers in electronic engineering and beyond. Whether students aim for a career in R&D, design, or system optimization, this contest helps them to stand out.

Asoc. Prof. Cristian-Marcel FĂRCAŞ, Ph.D.

Technical University of Cluj-Napoca

TIE<sub>TPLUS</sub> Technical Committee – Academic Trainers Chair

# The Technologies of Interconnection in Electronics (TIE) Industry wide student challenges: From Inspiration to Leadership in Packaging Design

The Technologies of Interconnection in Electronics (TIE) has been a cornerstone of my career, starting as a participant and eventually leading me to my current role as a Senior Packaging Engineer at a stealth company. As someone who has worked in various capacities, including Packaging Engineer at eSilicon and Inphi and Packaging Director at Marvell, I've seen firsthand how critical semiconductor packaging is to the development of modern electronics. TIE served as the initial source of inspiration for my journey into packaging engineering, and it continues to guide my work today as I help lead the technical committee for the contest.

#### The Role of TIE in Shaping My Career Path

My journey in packaging engineering started with TIE, where I was introduced to the complexities of interconnect design. The hands-on experience of designing functional interconnects and solving real-world design challenges fueled my passion for the field and shaped my career trajectory.

- 1. **Early Career:** TIE introduced me to interconnect design, laying the foundation for my work at eSilicon and Inphi, where I focused on power integrity, signal integrity, and electrical performance.

- Leadership at Marvell: As Packaging Director at Marvell, I led teams developing high-performance packaging solutions, applying TIE's principles to balance tradeoffs in size, speed, power, and integrity.

- Current Role: Now as Senior Packaging Engineer, I tackle next-gen packaging challenges in miniaturization and power integrity, with TIE's lessons still guiding my work.

Through my work on the technical committee, I now strive to provide that same inspiration to future generations of engineers. I understand the impact TIE can have on shaping students' careers, just as it did mine.

#### The Importance of Packaging in Modern Electronics

Semiconductor packaging is crucial for device performance, impacting signal integrity, power integrity, and power efficiency. These areas are core to the challenges faced in TIE:

- 1. Power Integrity: Packaging must ensure that power delivery is stable and efficient to maintain optimal performance, a key issue TIE participants address.

- 2. Signal Integrity: Maintaining the integrity of electrical signals in increasingly miniaturized circuits is another challenge participants work on, similar to my current role.

- Custom Layout: TIE participants work on custom layout techniques, designing tailored solutions for packaging challenges. These designs push the boundaries of what is possible in semiconductor packaging.

#### **Welcomes to TIE 2025 Event**

#### **How TIE Empowers the Next Generation of Packaging Engineers**

As a former TIE participant and now a leader on the technical committee, I can attest to the unique value of the contest. TIE serves as a platform not only for honing technical skills but also for developing a deep understanding of how packaging directly impacts the success of modern devices. Through TIE, students are exposed to the kinds of real-world challenges that I face daily in my career, making it an invaluable experience for anyone interested in packaging engineering.

- Hands-On Design Experience: The challenges in TIE mirror the real-world problems packaging engineers must solve. Students must take into account thermal management, electrical performance, cost constraints, and manufacturing processes. These experiences prepare participants for the complexities of the packaging industry, where every design decision can have farreaching consequences on performance and cost.

- 2. Networking and Industry Collaboration: TIE offers students the chance to interact with professionals in the packaging industry, providing exposure to cutting-edge tools, technologies, and best practices. As part of the technical committee, I ensure that students are connected with leading experts who can offer guidance and mentorship, furthering their development as future packaging engineers.

- 3. Encouraging Innovation and Problem Solving: The TIE contest encourages participants to think creatively, coming up with new ways to solve traditional packaging challenges. The industry is rapidly evolving, and the best solutions often come from unexpected places. I've seen firsthand how TIE participants' innovative approaches can lead to breakthroughs, pushing the boundaries of what's possible in semiconductor packaging.

#### Conclusion: TIE as the Starting Point for a Career in Packaging Engineering

The TIE contest is more than just a competition - it's a catalyst for the next generation of packaging engineers. For me, TIE was the spark that ignited my passion for semiconductor packaging, and it continues to inspire my work. The skills I developed through TIE set the foundation for my career in packaging.

As a member of the technical committee, I am excited to see how TIE participants will continue to innovate and shape the future of semiconductor packaging. For students in TIE, remember that the skills and knowledge you gain today will serve as the cornerstone for your future career in the ever-evolving field of packaging engineering. The work you do in TIE could be the next step in the future of electronics, and I look forward to seeing the breakthroughs you will create.

#### **Dan MANOLESCU**

APTE-Association for Promoting Electronics Technology TIEµ Technical Committee Chair

# TIEµ 2025 - second edition industry-wide student challenge

The beginning of 2025 marked my return to the TIE family, an opportunity I deeply cherish. My journey with the TIE (Interconnection Techniques in Electronics) student contest began in 2007 when I participated as a student in this prestigious competition, which aims to promote technological computer-aided design (CAE-CAD-CAM) of electronic modules among students.

Over the years, TIE has evolved beyond its initial  $TIE_E$  category, expanding to include  $TIE_{EPLUS}$ ,  $TIE_M$ , and  $TIE_T$ . Since last year, the competition has further broadened its focus by introducing  $TIE_H$  (Micro) — a premier student contest dedicated to microelectronics, advanced packaging, and electronic module design, emphasizing System-in-Package (SiP) technologies.

With the rapid advancement of semiconductor technology, the demand for **smaller**, **faster**, **and more efficient** electronic devices has never been greater. **TIE**µ provides

students with a unique platform to apply theoretical knowledge, refine practical skills, and push the boundaries of electronic packaging design. The competition fosters innovation, technical excellence, and collaboration between students, academia, and industry leaders.

By participating in **TIE**μ, students gain hands-on experience, showcase their expertise microelectronics, and contribute to the future of high-performance, electronic compact systems. Whether addressing power integrity challenges. enhancing signal integrity,

**optimizing designs for manufacturability**, TIEμ participants play a crucial role in **shaping the next generation of electronics**.

#### Lecturer Raul FIZESAN, Ph.D.

Technical University of Cluj-Napoca

TIEµ International Modelling & Simulation Environment

Coordinator

#### TIE - Life -changing experience

TIE experience represents a unique opportunity for participating students to validate their knowledge and skills to design electronic modules, in accordance with the real needs of the industry. Thus, the student has the chance to self-evaluate his professional level and, at the same time, he is able to predict the technical discussion topics from a future recruitment process. This is due to the fact that the contest subject is 100% oriented towards applicability and up-to-date engineering requirements. The experience of working under competitive pressure enriches the student's portfolio of lessons learned. I have summarized below, from the multitude of valuable lessons learned, two unique experiences I encountered at TIE:

- 1. Time relativity. I have always been passionate about science and have shown a lot of interest and curiosity about how things work around me, but I never imagined that I would understand what the concept of time relativity means by participating in TIE. How come? From the moment I received the TIE subject, I simply detach from everything that was happening around me. Four hours I managed to stay focused on solving the topic. I didn't see that somebody came and took pictures, I didn't even notice who was the competitor in front of me or that at some point he got up and left the room because his CAD tool encountered a "system crash". It was the most intense experience of perceiving time until then and I didn't feel it in any other competition or exam. Certainly for the evaluators and staff it was a long four hours journey, but we, the participants, felt that seconds turned into milliseconds and time flew by, giving the impression that it does not obey the same physical laws. After this unique experience, I felt that I could have given meditations on the relativity of time even to physics professor.

- 2. Ctrl+S... trivial, right? On my second participation in the competition (Sibiu 2012), I've learned a new lesson that I will never forget. In the pre-competition period, we were training with our mentor Adrian Petrariu, who used to say often: Save your layout progress! Don't forget to save your work! A good advice... For me, the stakes were high because a year before I had taken 2nd place and I wanted to surpass myself by aiming for 1st place. It was still the first edition where I participated in with a different CAD tool... and the inevitable happened: after 3 contest hours, while I was routing USB differential pairs, the image on the display froze and my laptop stopped responding to any command... software crash. My universe collapsed knowing that I hadn't saved anything on the layout side, and the CAD tool had no intermediate save option. Thus, I took the 12th place, but that experience helped me to avoid major inconveniences in my career as a design engineer. Create versions, constantly save the progress of your work!

#### Welcomes to TIE 2025 Event

It is undeniable that innovations in the field of electronics/micro-electronics can change a nation destiny, in the current global context. But the innovation process in this field is not efficient and sustainable without close collaboration between university educational centers and industry. Through TIE, 33 years ago, the foundations of this bridge was laid with the enormous contribution of the TIE People (committee, members, consultants, professors, volunteers, students and sponsors), making this event a benchmark. An international benchmark in the field of professional electronics capable to inspire other fields of engineering and beyond.

I wish the best of luck to all TIE 2025 participants!

Dorin ANTONOVICI

Director Development

ifm prover s.r.l.

ΤΙΕμ - Industrial Committee Member

#### **Event Committees 2025**

#### **Steering Committee**

**General Chair:**

Paul SVASTA, POLITEHNICA of Bucharest; Association for Promoting Electronics

Technology

**General Co-Chair:**

Ovidiu POP, Technical University of Cluj-Napoca

**General Academic Co-Chairs:**

Dan PITICĂ, Technical University of Cluj-Napoca

Norocel CODREANU, POLITEHNICA of Bucharest

**General Industrial Co-Chair:**

Cosmin MOISĂ, Continental Automotive, Timișoara

**Financial Chair:**

Alexandru VASILE, POLITEHNICA of Bucharest

TIE 2025 Chair:

Titus BĂLAN, Transilvania University of Brașov

TIE 2025 Co-Chair:

Cătălin CIOBANU, Transilvania University of Brasov

**Steering Committee Members:**

Dorel AIORDĂCHIOAIE, Dunărea de Jos University of Galaţi

Alexandru BORCEA, Romanian Association for Electronic and Software Industry

Radu BOZOMITU, Gh. Asachi Technical University of Iaşi

Vlad CEHAN, Gh. Asachi Technical University of Iasi

Gabriel CHINDRIS, Technical University of Cluj-Napoca

Cătălin CIOBANU, Transilvania University of Brașov

Philip COANDĂ, Continental Automotive Timișoara

Eugen COCA, Stefan cel Mare University of Suceava

Daniel COMEAGĂ, POLITEHNICA of Bucharest

Mircea-Cătălin CONSTANTINESCU, University of Craiova

Aurelia FLOREA, Miele Brașov

Aurel GONTEAN, Politehnica University of Timişoara

Tecla GORAŞ, Gh. Asachi Technical University of Iaşi

Georgiana GOTIA, Continental Automotive Systems Sibiu

Ciprian IONESCU, POLITEHNICA of Bucharest

Ioan LITĂ, POLITEHNICA of Bucharest, University Center of Pitești

Dan LASCU, Politehnica University of Timişoara

Marcel MANOFU, Continental Automotive Timisoara

Dan MANOLESCU, Association for Promoting Electronics Technology

Bogdan MIHĂILESCU, POLITEHNICA of Bucharest; APTE

Cătălin NEGREA, Darknote Engineering

Viorel NICOLAU, Dunărea de Jos University of Galați

#### **Event Committees 2025**

Cristina OPREA, Tensor srl

Gheorghe PANĂ, Transilvania University of Braşov

Mihaela PANTAZICĂ, POLITEHNICA of Bucharest

Daniela TĂRNICERIU, Gh. Asachi Technical University of Iași

Adrian TULBURE, 1 Decembrie 1918 University of Alba Iulia

Liviu VIMAN, Technical University of Cluj-Napoca

Gabriel VLĂDUŢ, Romanian Association for Technological Transfer and Innovation

Maria VINŢAN, Lucian Blaga University of Sibiu

#### **International Advisory Body:**

Karlheinz BOCK, TU Dresden, Electronics Packaging Lab IAVT, Dresden, Germany

Detlef BONFERT, Fraunhofer EMFT, Munich Germany

Joseph FJELSTAD, CEO of Verdant Electronics, USA

Zsolt ILLYEFALVI-VITEZ, University of Technology and Economics, Budapest, Hungary

Pavel MACH, Czech Technical University in Prague, Czech Republic

Alain MICHEL, ANSYS France

Jim MORRIS, Portland State University, Oregon USA

Andy SHAUGHNESSY, The PCB Design Magazine and PCBDesign007, USA

Nihal SINNADURAI, IMAPS ELC Past President, U.K.

Heinz WOHLRABE, TU Dresden, Germany

Klaus-Jürgen WOLTER, TU Dresden, Germany

#### **TIE Media Publisher Committee**

#### Chair:

Cătălina NEGHINĂ, Lucian Blaga University of Sibiu

#### Members:

Cristina LEPĂDATU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology

Bogdan MIHĂILESCU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology

Rodica NEGROIU, POLITEHNICA of Bucharest

Tamara SAUCIUC, POLITEHNICA Bucharest

Elena Mirela STETCO, Technical University of Cluj-Napoca

#### **Exposition Committee**

#### Chair:

Rajmond JÁNÓ, Technical University of Cluj Napoca, Romania

#### **Co-Chairs:**

Adelina-Ioana ILIEŞ, Technical University of Cluj Napoca, Romania

#### Member:

Cristina Mihaela LEPĂDATU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology, Romania

#### **Event Committees 2025**

#### **IEEE EPS Student Chapters Support Committee**

#### Chair:

Mădălin MOISE, IEEE-EPS, POLITEHNICA of Bucharest

#### Co-Chair:

Alexandra FODOR, IEEE-EPS, Technical University of Cluj-Napoca, SBC Chair

#### Members:

Mădălina-Irina BURCEA, IEEE-NTC, POLITEHNICA of Bucharest

Elisei ILIES, Politehnica University of Timisoara

Mihai NEGHINĂ, Lucian Blaga University of Sibiu

Rodica NEGROIU. IEEE-NTC. POLITEHNICA of Bucharest

Cosmin ONCIOIU, POLITEHNICA of Bucharest

Corina SĂNDULESCU, POLITEHNICA of Bucharest

Elena STETCO, Technical University of Cluj-Napoca

#### **Local Committee**

#### Chair:

Cătălin CIOBANU, Transilvania University of Brasov

#### Co-Chair:

Titus BĂLAN, Transilvania University of Brașov Vlad POPESCU, Transilvania University of Brasov

#### Members:

Corina Ioana BOGDAN, Transilvania University of Braşov Marius CARP, Transilvania University of Braşov Csaba Zoltán KERTÉSZ, Transilvania University of Braşov Traian TULBURE, Transilvania University of Brasov

#### **Technical secretariat**

#### Chair:

Delia LEPĂDATU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology

#### Members:

Cristina LEPĂDATU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology

Bogdan MIHĂILESCU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology

Maria PĂTULEANU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology

Florentina STĂLINESCU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology

#### Wednesday, April 2

| The participants are encouraged to attend any activity in any TRACK that would interest them  (except the ones marked as restricted) |                                                                                                                                                                        |                                                                                     |                                                                                                                                                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Time frame                                                                                                                           | Track 1 TECHNOLOGIES of INTERCONNECTIONS in ELECTRONICS the 34 <sup>th</sup> edition Industry-Wide Student Challenges                                                  |                                                                                     | Track 2 MICROELECTRONICS DAYS the 1st edition organized by the Working Group for Microelectronics of the STMS Comission of the Romanian Academy |  |

| JOINT EV                                                                                                                             | ENTS WITH THE RE                                                                                                                                                       | GIONAL DEVELOPME                                                                    | NT AGENCY – CENTRU                                                                                                                              |  |

| 09:00 – 14:30                                                                                                                        | Registra                                                                                                                                                               | tion & Exhibition opening<br>(1 <sup>st</sup> floor hall)                           | - Welcome coffee                                                                                                                                |  |

| 10:00 – 12:00                                                                                                                        | Workshop ADR Centru (EEN) (Amphitheater) Intellectual Property and Intellectual Property Rights                                                                        |                                                                                     | WEHUB Digital Chiplets and Heterogeneous Integration for Innovative Companies (Amphitheater)                                                    |  |

| 12:00 – 12:15                                                                                                                        |                                                                                                                                                                        | Coffee Break<br>(1 <sup>st</sup> floor hall)                                        |                                                                                                                                                 |  |

| 12:15 – 14:00                                                                                                                        | Workshop ADR Centru (EEN) (Amphitheater) Integration of regional organizations into European initiatives and partnerships in the field of electronics/microelectronics |                                                                                     | WEHUB Digital Chiplets and Heterogeneous Integration for Innovative Companies (Amphitheater)                                                    |  |

| 13:00 – 14:00                                                                                                                        | TIE <sub>EPLUS</sub> Final Stage (public event) (Amphitheater)                                                                                                         |                                                                                     | Workshops or ad-hoc meetings between direct and indirect participants in IPCEI or other collaborative projects (UI2, UI3, UI6 Rooms)            |  |

| 14:00 – 15:00                                                                                                                        | Light Lunch (1 <sup>st</sup> floor hall)                                                                                                                               |                                                                                     |                                                                                                                                                 |  |

| 15:00 – 18:00                                                                                                                        | TIEEPLUS Final Stage (public event) (Amphitheater)                                                                                                                     | Technical meetings (UI7 Room)                                                       | Workshops or ad-hoc                                                                                                                             |  |

| 18:00 – 18:30                                                                                                                        | Coffee Break<br>(1 <sup>st</sup> floor hall)                                                                                                                           | Steering Committee<br>Meeting<br>(RESTRICTED to<br>Committee members)<br>(UI7 Room) | meetings between direct and indirect participants in IPCEI or other collaborative projects (UI2, UI3, UI6 Rooms)                                |  |

| 18:30 – 19:00                                                                                                                        | propo<br>(Ampl                                                                                                                                                         | g the resolution of the<br>sed topics<br>nitheater)                                 |                                                                                                                                                 |  |

| 19:00                                                                                                                                | Welcome cocktail and expo networking (1st floor hall)                                                                                                                  |                                                                                     |                                                                                                                                                 |  |

#### Thursday, April 3

The participants are encouraged to attend any activity in any TRACK that would interest them (except the ones marked as restricted)

|            | • •                              | •                                  |

|------------|----------------------------------|------------------------------------|

| Time frame | Track 1 TECHNOLOGIES of          | Track 2 MICROELECTRONICS DAYS      |

|            | INTERCONNECTIONS in              | the 1 <sup>st</sup> edition        |

|            | ELECTRONICS                      | organized by the Working Group for |

|            | the 34 <sup>th</sup> edition     | Microelectronics of the STMS       |

|            | Industry-Wide Student Challenges | Commission of the Romanian Academy |

#### JOINT EVENTS WITH THE REGIONAL DEVELOPMENT AGENCY - CENTRU

|               | Registration - Welcome coffee         |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|---------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08:00 – 14:00 |                                       |                                       | loor hall)                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 08:30 - 09:00 | TIE <sub>MPLUS</sub> Final            | TIE <sub>TPLUS</sub> Final            | Welcome speech – The Romanian Academy The Position of the Romanian Academy "The National Ecosystem of Micro and Nano Electronics" (Amphitheater) Prof. Gheorghe ŞTEFAN – Corresponding Member of the Romanian Academy, President of the STMS Commission of the Academy Welcome speech – Transilvania University of Braşov Prof. Ioan Vasile ABRUDAN, Rector Welcome speech – Regional Development Agency ADR Centru Simion CREŢU – General Manager |

| 09:00 – 09:15 | Stage<br>(public event)<br>(UI2 Room) | Stage<br>(public event)<br>(UI3 Room) | Introduction to the Agenda of the day<br>Moderator: Prof. Adrian IONESCU –<br>STMS Commission, Romanian<br>Academy                                                                                                                                                                                                                                                                                                                                 |

| 09:15 – 10:00 |                                       |                                       | EU strategies reflected in EU and national programs (Amphitheater) Round table: Prof. Tudor PRISECARU, President of the Senate of the POLITEHNICA Bucharest Prof. Carmen BUZEA, Vice-Rector of the Transilvania University of Braşov Prof. Titus BĂLAN, Dean of the Faculty of Electrical Engineering and Computer Science, Transilvania University of Braşov Dr. Andreas WILD, STMS Comission,                                                    |

#### **TIE 2025 Event Agenda**

| 10:00 – 10:15<br>10:15 – 10:30 | Coffee I                                                   |                                                                     | Romanian Academy Dr. Paul Andrei PĂUN, "Mihai Drăgănescu" Research Institute for AI Moderators: Dr. Christian von ALBRICHSFELD, Former Country Head of Continental Romania and R&D Head  10:00 – 10:30 - Coffee Break (1st floor hall)                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:30 – 11:45<br>11:45 – 12:15 | TIE <sub>MPLUS</sub> Final Stage (public event) (UI2 Room) | TIE <sub>TPLUS</sub> Final<br>Stage<br>(public event)<br>(UI3 Room) | The National Platform of Semiconductor Technologies, PNTS (Amphitheater) Dr. Andrei AVRAM – Technical Director IMT IPCEI, the actual status in Romania • The progress reached by the direct participants Speakers: representatives of Bosch, NXP, Continental • The status of the indirect participants Speakers: representatives of project coordinators in universities, research institutes and small and medium enterprises  A national ecosystem in micro and nanoelectronics (1) (Amphitheater) Keynote: the contest "Tudor Tănăsescu", a complementary mean for the development of highly |

|                                |                                                            | ,                                                                   | qualified specialists  Prof. Gheorghe BREZEANU –  Politehnica of Bucharest  unch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12:15 – 13:15                  |                                                            |                                                                     | loor hall)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13:15 – 15:00                  | TIEμ Final Stage (public event)<br>(UI6 Room)              |                                                                     | Complementary actions for Chips-JU (Amphitheater)  • Pilot lines Prof. Marius ENĂCHESCU — Politehnica Bucharest Financing the development of research and innovation activities carried out by the business environment by using European funds during 2021-2027 — ADR Centru                                                                                                                                                                                                                                                                                                                    |

| 15:00 – 15:15 | Coffee Break<br>(1st floor hall)              |                                       |                                      | Contribution of RDA/RP Center     2021-2027 to the STEP Platform     Other EU and international initiatives     Prof. Adrian IONESCU – STMS     Commission, Romanian Academy      14:45 – 15:15 - Coffee Break     (1st floor hall)  Bench A patiental accounters in micro.                                                                                                                                                                                                                                                                                               |

|---------------|-----------------------------------------------|---------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | TIEμ Final Stage (public event)<br>(UI6 Room) |                                       | ic event)                            | Panel: A national ecosystem in micro-<br>and nanoelectronics (2)<br>(Amphitheater)<br>Coordination of the National<br>Ecosystem:<br>Răzvan Crăciunescu, Prodean at<br>Faculty of Electronics,                                                                                                                                                                                                                                                                                                                                                                             |

| 15:15 – 17:00 |                                               | Assessment<br>CTED to Com<br>members) |                                      | Telecommunications and Information Technology, representatives of Mihnea COSTOIU, Rector Politehnica Bucharest  Coordination with other national                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               | TIE <sub>MPLUS</sub><br>(UI2<br>Room)         | TIE <sub>TPLUS</sub><br>(UI3<br>Room) | TIEµ<br>(UI7<br>Room)                | programs and activities (such as "Tudor Tănăsescu" contest, Technologies of Interconnections in Electronics – Industry-Wide Student Challenges, a.s.o)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17:00 – 17:45 | Tecl<br>TIE <sub>E</sub><br>(UI2+UI3 R        | nnical Meeti                          | ngs<br>TIE <sub>M</sub><br>UI6 Room) | Establishing a formal group for contacts with the Romanian authorities with periodical meetings  Research and innovations in  European and regional strategies to increase the SME competitiveness, with emphasis on the funding offered through the 2021-2027  Ioan LEVITCHI – Director of the Regional Policies Department, ADR Centru  Development of research and innovation in universities in Centru Region, with the support of European funds  Prof. Ana-Maria CAZAN, Dean of the Faculty of Psychology and Education Sciences, Transilvania University of Braşov |

#### TIE 2025 Event Agenda

|               | Synergies between PR Centru and European Partnerships for Innovation Iceberg Consulting Session conclusions Moderators: Prof. Adrian IONESCU – STMS Commission, Romanian Academy Ovidia CABA – Director of the Department Regional Policies and Programs, ADR Centru |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 17:45 – 18:45 | Common Session: TIEµ, TIE <sub>M PLUS</sub> si TIE <sub>T PLUS</sub> Demystifying the resolution of the proposed topics (Amphitheater)                                                                                                                               |  |

| 18:45 – 20:30 | Award Ceremony  Keynote1: Victoria CUMMINGS – ECSA, EU Chips-Skill Academy  Keynote 2: Carolyn TUBILLO – Cadence, EDA solutions  (Amphitheater)                                                                                                                      |  |

| 20:30         | Gala dinner<br>(Sergiana Center)                                                                                                                                                                                                                                     |  |

| 21:30         | TIE Committee Chairs & European Chips Skills Academy representatives meeting (RESTRICTED) (UI7 Room)                                                                                                                                                                 |  |

#### Friday, April 4

The participants are encouraged to attend any activity in any TRACK that would interest them (except the ones marked as restricted)

|            | (checks and check man        |                    |

|------------|------------------------------|--------------------|

|            | Track 1                      |                    |

|            | TECHNOLOGIES of              |                    |

|            | INTERCONNECTIONS in          | MICROEI            |

| Time frame | ELECTRONICS                  | th<br>organized by |

|            | the 34 <sup>th</sup> edition | Microelectronic    |

|            | Industry-Wide Student        | the Ro             |

|            | Challenges                   |                    |

### MICROELECTRONICS DAYS the 1st edition

Track 2

organized by the Working Group for Microelectronics of the STMS Comission of the Romanian Academy

#### JOINT EVENTS WITH THE REGIONAL DEVELOPMENT AGENCY - CENTRU

|               | Preliminar                                 | y activities                                | Registration for Microelectronics Day 2 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|--------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08:00 - 08:30 | TIEE                                       | TIEM                                        | welcome coffee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               | (UI2+UI3<br>Rooms)                         | (UI6 Room)                                  | (1st floor hall)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 08:30 - 08:40 |                                            |                                             | Opening session: Wrap-up day 1 (Amphitheater)  Prof. Adrian IONESCU – STMS Comission, Romanian Academy  Dr. Andreas WILD – STMS Comission, Romanian Academy                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 08:40 - 08:50 |                                            |                                             | Introduction on the Agenda of the day (Amphitheater)  Moderator:  Prof. Paul SVASTA – STMS Comission, Romanian Academy  Prof. Ovidiu POP – STMS Comission, Romanian Academy                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 08:50 – 10:00 | TIE <sub>E</sub> Hackathon (UIZ+UI3 Rooms) | TIE <sub>M</sub><br>Hackathon<br>(UIG Room) | A National Ecosystem in Micro and Nano Electronics (3) (Amphitheater)  ADR Centru: Education and vocational training in smart specialization areas in the Center Region Program Priority 1, 2 and 6  Ovidia CABA – ADR Centru  CNDIPT – Dual education in the Center Region  Gabriel RADU – ADR Centru  Partnership for Education – Academic & Economic Environment  Aurelia FLOREA – MIELE Tehnica Braşov  Transilvania University of Braşov - Cooperation between universities and bussiness environment  Prof. Titus BĂLAN, Dean of the Faculty of Electrical Engineering and Computer Science, Transilvania University of Braşov |

#### TIE 2025 Event Agenda

| 10:00 – 10:30 |                                                                                                                 |                                                         | Braşov City Hall: Regional Integrated Consortium for Dual Education Braşov, initiative to create a complete professional route for higher technical education  Coffee Break, opportunity to visit TIE <sub>E</sub> & TIE <sub>M</sub> Hackathon activities (1st floor hall) |

|---------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:30 – 12:30 |                                                                                                                 |                                                         | TIEµ: a complementary instrument for future professional education (Amphitheater)  Assoc. Prof. Cătălin CIOBANU – Transilvania University of Braşov  International Panel: Skills Development in Electronics Packaging (Amphitheater)                                        |

| 12:30 – 13:30 |                                                                                                                 |                                                         | Participants: Victoria CUMMINGS – ECSA,<br>EU Chips-Skill Academy representative; Dr.<br>Peter TRANITZ – IPC EU Silicon to Systems;<br>Romanian delegates                                                                                                                   |

| 13:30 –14:00  | TIE <sub>E</sub> Assessments (public events) (UI2+UI3                                                           | TIE <sub>E</sub> Assessments (public events) (UI6 Room) | Ist floor hall)  Transfer from Transilvania University of Braşov Library to Miele Tehnica Braşov Coordinator: Aurelia FLOREA – Organizational Development & People Experience Director, Miele Tehnica Braşov                                                                |

| 14:00 – 16:30 | Rooms)                                                                                                          | , ,                                                     | Visit at the Miele Tehnica Brașov                                                                                                                                                                                                                                           |

| 18:30 – 19:00 | TIE Steering Committee & Microelectronics Representatives Meeting (RESTRICTED to Committee members)  (UI7 Room) |                                                         |                                                                                                                                                                                                                                                                             |

|               | Awarding TIE <sub>E</sub> , TIE <sub>M</sub> & Conclusion speeches                                              |                                                         |                                                                                                                                                                                                                                                                             |

| 19:00         | (Amphitheater) Closure Banquet (Sergiana Center)                                                                |                                                         |                                                                                                                                                                                                                                                                             |

| Saturday, April 5 |                                                                      |  |

|-------------------|----------------------------------------------------------------------|--|

|                   | Looking Forward.                                                     |  |

| 09:30 - 10:30     | Farwell discussion for the next TIE Industry-wide student challenge, |  |

| 09.30 - 10.30     | TIE 2026                                                             |  |

|                   | (1st floor hall)                                                     |  |

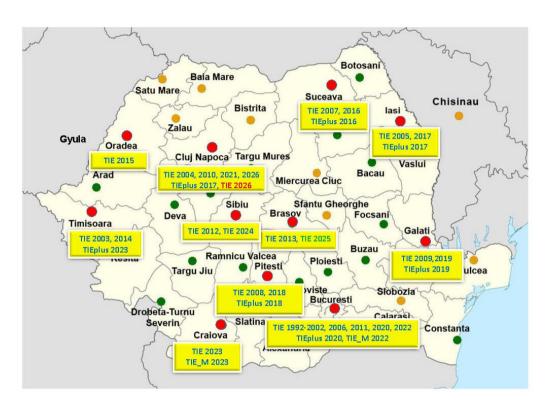

#### TIE past present and future editions

| Year      | University                              | Event |

|-----------|-----------------------------------------|-------|

| 1992-2002 | University Politehnica of Bucharest     | TIE   |

| 2003      | Politehnica University of Timişoara     | TIE   |

| 2004      | Technical University of Cluj-Napoca     | TIE   |

| 2005      | Gh. Asachi Technical University of Iaşi | TIE   |

| 2006      | University Politehnica of Bucharest     | TIE   |

| 2007      | Ştefan cel Mare University of Suceava   | TIE   |

| 2008      | University of Piteşti                   | TIE   |

| 2009      | Dunărea de Jos University of Galaţi     | TIE   |

| 2010      | Technical University of Cluj-Napoca     | TIE   |

#### TIE & TIEM & TIEPLUS past and present editions

| 2011 | University Politehnica of Bucharest     | TIE                                                         |

|------|-----------------------------------------|-------------------------------------------------------------|

| 2012 | Lucian Blaga University of Sibiu        | TIE                                                         |

| 2013 | Transilvania University of Braşov       | TIE                                                         |

| 2014 | Politehnica University of Timişoara     | TIE                                                         |

| 2015 | University of Oradea                    | TIE,                                                        |

|      |                                         | TIE <sub>Plus</sub> Kick-off                                |

| 2016 | Ştefan cel Mare University of Suceava   | TIE, TIE <sub>Plus</sub>                                    |

| 2017 | Gh. Asachi Technical University of Iaşi | TIE, TIEPlus                                                |

| 2018 | University of Piteşti                   | TIE, TIE <sub>Plus</sub>                                    |

|      |                                         | 1 <sup>st</sup> TIE bootcamp                                |

| 2019 | Dunărea de Jos University of Galaţi     | TIE, TIEPlus                                                |

| 2020 | University Politehnica of Bucharest -   | TIE, TIE <sub>Plus</sub>                                    |

|      | Virtual Event                           | ,                                                           |

| 2021 | Technical University of Cluj-Napoca -   | TIE, TIE <sub>Plus</sub>                                    |