TIE-M -Mechanical

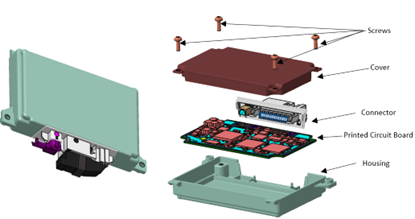

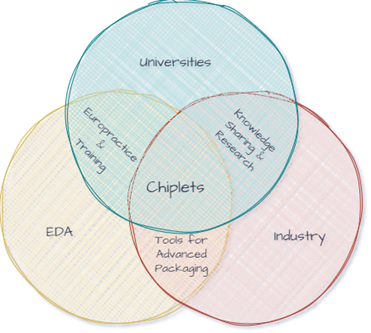

TIE M-Mechanical is a CAD Design Challenge that aims to assess students’ proficiency in computer-aided design (CAD) for mechanical components, with a focus on electronic packaging and electro-mechanical assembly as shown in Figure 1. This challenge evaluates students’ knowledge and skills acquired through coursework in mechanical engineering, emphasizing the design and manufacturing of mechanical components using CAD software. The challenge seeks to establish itself as a benchmark certification in the field of mechanical CAD design, particularly within the context of electronic packaging and electro-mechanical systems.

Figure 1. Electro-mechanical assembly

Objectives:

– Stimulating student’s interest in mechanical engineering and CAD design, particularly in the context of electronic packaging and electro-mechanical assembly.

– Evaluating student’s CAD design skills within a competitive framework, fostering a spirit of excellence and innovation in mechanical component design for electronic systems.

– Certifying student’s CAD proficiency endorsed by industry experts, including the Industrial -Advisory Committee (IAC), to meet industry standards and requirements for electronic packaging and electro-mechanical assembly.

– Providing the electronics industry with a pool of skilled CAD designers ready to contribute to various electro-mechanical engineering projects, including electronic packaging solutions.

– Familiarizing students with the processes involved in designing mechanical components and assemblies for electronic packaging, ensuring compatibility with electronic modules and adherence to packaging standards.

– Cultivating a high level of professionalism in the use of CAD software systems for mechanical engineering applications in the context of electronic packaging and electro-mechanical assembly.

– Increasing awareness within the mechanical engineering and electronics industries about available talent and fostering strong partnerships between academia and industry in the realm of electro-mechanical engineering.

– Generating increased demand for mechanical engineers with CAD design skills specialized in electronic packaging and electro-mechanical assembly among current students and expanding job opportunities within the industrial sector.

Description of a subject (summary)

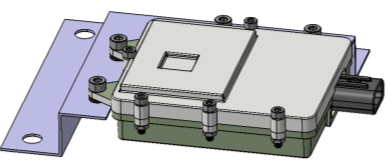

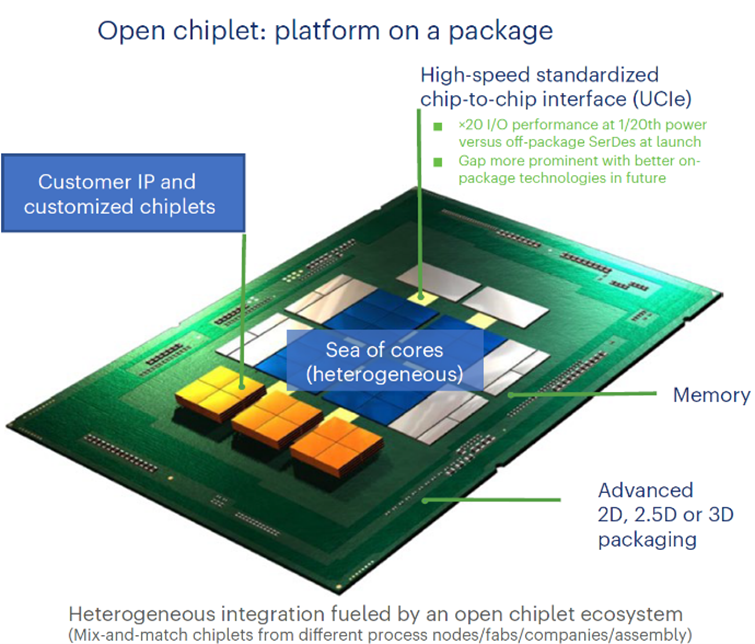

As a mechanical design engineer, your company won a project to create a sensor module for a well know OEM car manufacturer. To boost profits and speed up development, the company chose to use existing components (Figure 2) and make design ajustments to meet the client’s needs. Modifications to the bracket and sensor ensure they fit within specified areas without altering overall functionality. The client provided a 2D drawing (“Cover.pdf”) as a starting point for the cover design, which must be optimized to meet all requirements. The 3D model includes restricted areas for the new parts.

Figure 2 Existing components

Solution

The criteria on the basis of which the student qualifies as being initiated in the evaluated topic:

– Understanding Electronic Packaging: Show knowledge of how to place electronic components and manage heat within CAD designs.

– Efficient Component Integration: Ability to seamlessly integrate electronic parts into mechanical designs while meeting industry standards.

– CAD Proficiency: Expertise in using CAD software to design, model, and simulate electronic assemblies.

– Creative Problem-Solving: Demonstrate innovative solutions to electronic packaging challenges within CAD designs.

– Detail-Oriented Design: Attention to detail in CAD designs, including precision in measurements, accurate placement of components, and consideration of assembly constraints and tolerances for electronic packaging.

– Compliance with Standards: Ensure that CAD designs meet industry standards and client requirements.

– Clear Communication: Clearly convey design intentions through CAD drawings and documentation for effective collaboration.

– Professionalism: Maintain professionalism by meeting deadlines, accepting feedback, and handling information ethically.

|

|

|

| Alina Spânu, POLITEHNICA Bucuresti | Alexandru Falk, Continental Autonomous Mobility |