| Wednesday, April 24 | ||

| 09:00 – 19:00 | Registration | Hall of the Faculty of Medicine |

| 10:00 – 11:00 | Welcome speech | Library, 3rd floor hall |

| 11:00 – 12:00 | Technical meeting TIE Eplus, TIE Mplus, TIE Tplus, TIEμ | Library, 3rd floor hall |

| 12:00 – 13:00 | Lunch | Library, Private Area (ground floor) |

| 13:00 – 17:00 | TIE Eplus contest | Library, Internet Room (ground floor) |

| 13:00 – 17:00 | TIE Mplus contest | Library 3rd floor hall |

| 13:00 – 17:00 | TIE Tplus contest | Library, Room 314 (3rd floor) |

| 17.00 – 17.15 | Coffee Break | Library, Private Area (ground floor) |

| 17:15 – 18:00 | TIE Eplus Committee Assessment meeting | Library, Internet Room (ground floor) |

| 17:15 – 18:00 | TIE Mplus Committee Assessment meeting | Library, Multimedia Room (3rd floor) |

| 17:15 – 18:00 | TIE Tplus Committee Assessment meeting | Library, Room 314 (3rd floor) |

| 18:15 – 19:30 | Steering Committee Meeting | Library, Room 314 (3rd floor) |

| 21.00 | Dinner | My Continental Hotel |

| Thursday, April 25 | ||

| 08:15 – 14:00 | Welcome & Registration | Hall of the Faculty of Medicine |

| 08:45 – 10:45 | CAD Activities in Education and Training – WORKSHOP on Multiphysics Approach | Aula Magna |

| 10.45 – 11.00 | Coffee Break | Library, Private Area (ground floor) |

| 11:00 – 12:00 | CAD Activities in Education and Training – WORKSHOP on Multiphysics Approach | Aula Magna |

| 12:00 – 13:00 | Lunch | Library, Private Area (ground floor) |

| 13:00 – 16:00 | TIE μ contest – First edition | Library, Room 314 (3rd floor) |

| 16.00 – 16.15 | Coffee Break | Library, Private Area (ground floor) |

| 16:15 – 17:00 | TIE μ Committee Assessment meeting | Library, Room 314 (3rd floor) |

| 17:00 – 18:00 | Industrial Session | Aula Magna |

| 17:00 – 18:00 | Steering Committee Meeting | Library, Internet Room (ground floor) |

| 18:00 – 19:00 | Awarding TIEplus’s and TIEμ | Aula Magna |

| 19:00 – 20:30 | Technical meeting TIE E, TIE M | Aula Magna |

| 21:00 | Dinner | My Continental Hotel |

| Friday, April 26 | ||

| 07:30 – 08:00 | TIE E, TIE M preliminary activities | |

| 08:00 – 12:30 | TIE E contest | Library 3rd floor hall |

| 08:00 – 12:30 | TIE E committee evaluation scaling | Library, Room 314 (3rd floor) |

| 08:00 – 12:30 | TIE M contest | Library, Internet Room (ground floor) |

| 08:00 – 12:30 | TIE M committee evaluation scaling | Library, Private Room (ground floor) |

| 12:30 – 13:30 | Lunch | Library, Private Area (ground floor) |

| 13:30 – 18:00 | Assessments | Library, 3rd floor hall, Internet Room |

| 18:00 – 19:00 | Steering Committee Meeting | Aula Magna |

| 19:30– 20:30 | Awarding TIE E, TIE M | Aula Magna |

| 21.00 | Gala dinner | My Continental Hotel |

| Saturday, April 27 | ||

| 09:00 | Sibiu City Tour | |

2024

TIE-µ: a new TIE topic launching in 2024

Welcome to the TIE-µ

Gordon Moore famously predicted in his” Moore’s Law” paper that it might become more cost-effective to construct extensive systems using smaller, individually packaged functions interconnected together. More than half a century later, the structure of the System-on-a-Chip (SoC) changes significantly with the partitioning of a monolithic die into smaller chiplets: packaging becomes one of the main focuses when designing a chip and the way the initial functionality is partitioned between multiple chiplets and how these are interconnected means we must shift our perspective to Systems in Package (SiP) (source: A. Jâjâie, A. Puşcaşu, I. Ailenei, C. B. Ciobanu and P. Svasta, “Chiplets and Next-gen Packaging Technologies in University Education,” 2023 IEEE 29th International Symposium for Design and Technology in Electronic Packaging (SIITME), Craiova, Romania, 2023, pp. 207-214, https://doi.org/10.1109/SIITME59799.2023.10431355)

As the industry shifts towards heterogeneous integrations, systems in package and chiplets it becomes of paramount importance to train future engineers in these state-of-the-art techniques, including employing interposers, 2.5D, and 3D integration.

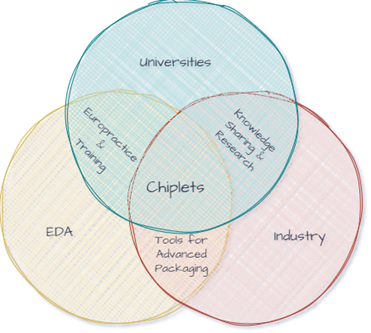

Starting from this year, TIE introduces a new topic – TIE-μ, which is addressing important subjects such as advanced packaging, 2.5D/3D integration and chiplets. In this regard, TIE is a unique approach and to our knowledge the only one of this type in Europe which bridges the gap between Universities, Industry and advanced topics such as Chiplets as shown in Figure 1. The contest brings all stakeholders to the table, ensuring industry relevant data sets are proposed as topics using state of the art EDA tools in an academic environment, in order to introduce future engineers to an upcoming future career path in advanced packaging, chiplet integration and heterogenous design.

Figure 1 Interaction between Industry, Universities and Chiplets

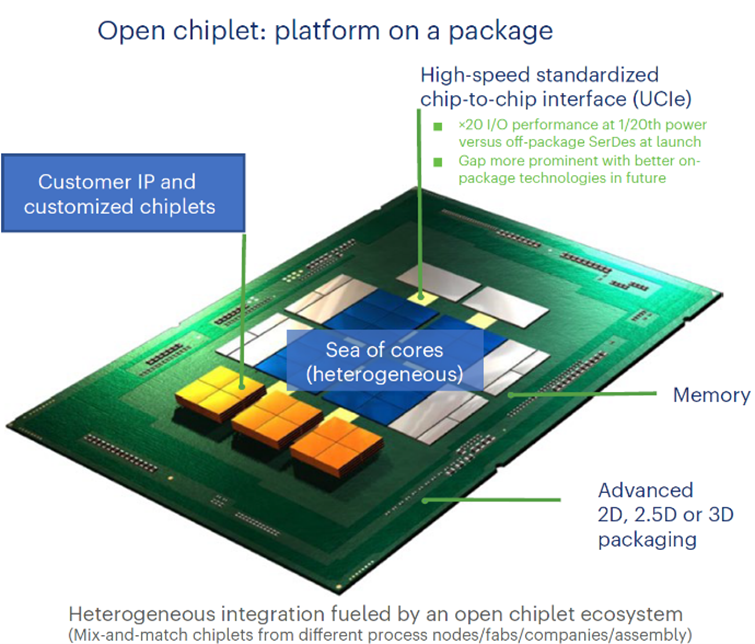

As illustrated in Figure 2 (source: https://www.nature.com/articles/s41928-024-01126-y), the modern approach for heterogenous integration requires high speed interfaces such as Universal chiplet interconnect express (UCIe) and advanced packaging. TIE-μ focuses on the new interconnection challenges for high-speed interfaces, interposers and other techniques the students need to prepare for when transitioning from SoC to SiPs. SiPs make use of specialized chiplets with customer IP and memory on the same package.

Figure 2 Heterogeneous open chiplet on-package

For sponsoring the event and obtain valuable networking experience, please visit TIE 2024 Partners and Sponsors.

TIE-E Plus Contest Regulation

- General

The present document outlines the primary factors to consider prior to and after enrollment in the TIE-E Plus competition. We would kindly ask you to read it thoroughly and for any questions you may have that are not directly addressed in the following lines you can always reach up to us at tieplus@up-see.org, and one member in the organizing committee will get back to you as soon as possible. We are dedicated to ensuring your successful participation at the event and facilitating your up-skilling process within our virtual prototyping community.

- Brief description

TIE-E Plus Contest is a prestigious competition established by industry professionals in collaboration with academia, with the main goal of driving froward innovative practices in engineering education, particularly focused on product virtual prototyping methods and techniques.Our objective is to help you understand current industry challenges and support you in becoming the engineer of tomorrow. We look to achieve this by exposing you to the latest technologies and industry product requirements. Thus, TIE-E Plus draws inspiration from real-life engineering challenges brought up by our industry partners and has as main goal to give you the chance to evaluate your engineering skill set against actual electronic product development challenges.

- Contestant profile requirements

The contestant must be enrolled at a higher education institution. Accepted profiles will fall under one of the following categories:

- Undergraduate students

- Graduate students

- Master’s students

- PhD Students

All applications will be verified by the organizing committee members. As soon as that happens you will get notified of the status of your application.Besides that, the contestant shall have a minimum idea about the contest’s scope and show at least basic skills using the tools needed to solve the proposed subject.Knowledge of English language (B1 level at least) is mandatory, as the subject presentation, trainings, and final report are/shall be written in English.

- Workflow

Further, a step-by-step guide for registering will be presented.

- First, identify the section you want to register to: Signal and Power Integrity, Thermal Management or Structural Analysis

- Fill in the registration form with the requested information.

- An acceptance or rejection notice will be sent to you.

- You will receive in your acceptance email the links to the specific group for your section. Please register and join the indicated group.

- During the solving period you’ll have access to a database of knowledge prepared by the technical committee members and a series of workshops. Feel free to join discussions and debates related to the subject.

- Solve the subject and create a report, considering the guidelines of each subject. Please remember that the quality of the report plays a major role in the evaluation.

- Upload the finished report and wait for our notification to see if you qualify to the next phase.

- Finalists will give a brief presentation on the 24th of April, live, in Sibiu, where they shall defend their approach, with arguments and examples, debating together with the committee.

Please be aware that the quality of your presentation plays a major role in the overall final evaluation. The preliminary results after the initial report analysis may change drastically after the final presentation.We encourage collaboration and discussions with academic coordinators or other peers, yet we do not tolerate cheating. Do not upload a solution that was not developed by you, as we will find out later, during live presentations.Good luck!

Event Committees 2024

Steering Committee

General Chairs:

Paul SVASTA, POLITEHNICA of Bucharest; Association for Promoting Electronics Technology Bucharest

Ovidiu POP, Technical University of Cluj-Napoca

General Academic Co-Chairs:

Dan PITICĂ, Technical University of Cluj-Napoca

Norocel CODREANU, POLITEHNICA of Bucharest

General Industrial Co-Chair:

Cosmin MOISĂ, Continental Automotive, Timişoara

Financial Chair:

Alexandru VASILE, POLITEHNICA of Bucharest

TIE 2024 Chair:

Maria VINTAN, Lucian Blaga University of Sibiu

TIE 2024 Co-Chair:

Mihai NEGHINA, Lucian Blaga University of Sibiu

Steering Committee Members:

Dorel AIORDĂCHIOAIE, Dunărea de Jos University of Galaţi

Alexandru BORCEA, Romanian Association for Electronic and Software Industry

Radu BOZOMITU, Gh. Asachi Technical University of Iaşi

Vlad CEHAN, Gh. Asachi Technical University of Iaşi

Gabriel CHINDRIŞ, Technical University of Cluj-Napoca

Cătălin CIOBANU, Universitatea Transilvania din Brasov

Philip COANDA, Continental Automotive, Timişoara

Eugen COCA, Ştefan cel Mare University of Suceava

Daniel COMEAGA, POLITEHNICA of Bucharest

Mircea-Cătălin CONSTANTINESCU, University of Craiova

Aurelia FLOREA, Human Resources Manager, Miele Brașov

Aurel GONTEAN, Politehnica University of Timişoara

Tecla GORAŞ, Gh. Asachi Technical University of Iaşi

Georgiana GOTIA, Continental Automotive Systems, Sibiu

Ciprian IONESCU, POLITEHNICA of Bucharest

Ioan LIŢĂ, POLITEHNICA of Bucharest, University Center of Piteşti

Dan LASCU, Politehnica University of Timişoara

Marcel MANOFU, Continental Automotive, Timişoara

Dan MANOLESCU, Marvell Technology Romania

Bogdan MIHĂILESCU, POLITEHNICA of Bucharest; APTE

Cătălin NEGREA, Darknote Engineering

Viorel NICOLAU, Dunărea de Jos University of Galaţi

Cristina OPREA, Tensor srl

Gheorghe PANĂ, Transilvania University of Braşov

Mihaela PANTAZICĂ, POLITEHNICA of Bucharest

Daniela TĂRNICERIU, Gh. Asachi Technical University of Iaşi

Adrian TULBURE, 1 Decembrie 1918 University of Alba Iulia

Liviu VIMAN, Technical University of Cluj-Napoca

Gabriel VLĂDUŢ, Romanian Association for Technological Transfer and Innovation

Maria VINTAN, Lucian Blaga University of Sibiu

International Advisory Body:

Karlheinz BOCK, TU Dresden, Electronics Packaging Lab IAVT, Dresden, Germany

Detlef BONFERT, Fraunhofer EMFT, Munich Germany

Joseph FJELSTAD, CEO of Verdant Electronics, USA

Zsolt ILLYEFALVI-VITEZ, University of Technology and Economics, Budapest, Hungary

Pavel MACH, Czech Technical University in Prague, Czech Republic

Alain MICHEL, ANSYS France

Jim MORRIS, Portland State University, Oregon USA

Andy SHAUGHNESSY, The PCB Design Magazine and PCBDesign007, USA

Nihal SINNADURAI, IMAPS ELC Past President, U.K.

Heinz WOHLRABE, TU Dresden, Germany

Klaus-Jürgen WOLTER, TU Dresden, Germany

IEEE EPS Student Chapters Support Committee

Chair:

Mădălin MOISE, IEEE-EPS, POLITEHNICA of Bucharest

Co-Chair:

Alin GRAMA, IEEE-EPS, Technical University of Cluj-Napoca, SBC Chair

Members:

Mădălina-Irina BURCEA, IEEE-NTC, POLITEHNICA of Bucharest

Anda JÂJÂIE, POLITEHNICA of Bucharest

Elisei ILIEȘ, Politehnica University of Timişoara

Mihai NEGHINĂ, Lucian Blaga University of Sibiu

Rodica NEGROIU, IEEE-NTC, POLITEHNICA of Bucharest

Cosmin ONCIOIU, POLITEHNICA of Bucharest

Corina SĂNDULESCU, POLITEHNICA of Bucharest

Elena STETCO, Technical University of Cluj-Napoca

Local Committee

Chair:

Mihai NEGHINĂ, Lucian Blaga University of Sibiu

Co-Chair:

Radu PETRUȘE, Lucian Blaga University of Sibiu

Members:

Iulian BOULEANU, Lucian Blaga University of Sibiu

Macarie BREAZU, Lucian Blaga University of Sibiu

Beriliu ILIE, Lucian Blaga University of Sibiu

Marinela INŢĂ, Lucian Blaga University of Sibiu

Daniel MORARIU, Lucian Blaga University of Sibiu

Cătălina NEGHINĂ, Lucian Blaga University of Sibiu

Antoniu PITIC, Lucian Blaga University of Sibiu

Technical secretariat

Chair:

Delia LEPĂDATU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology Bucharest

Members:

Carmen BUGNAR, Association for Promoting Electronics Technology Buchares

Cristina LEPĂDATU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology Bucharest

Bogdan MIHĂILESCU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology Bucharest

Maria PĂTULEANU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology Bucharest

Florentina STĂLINESCU, POLITEHNICA of Bucharest, Association for Promoting Electronics Technology Bucharest

TIE-Mplus REGISTRATION FORM (click here)

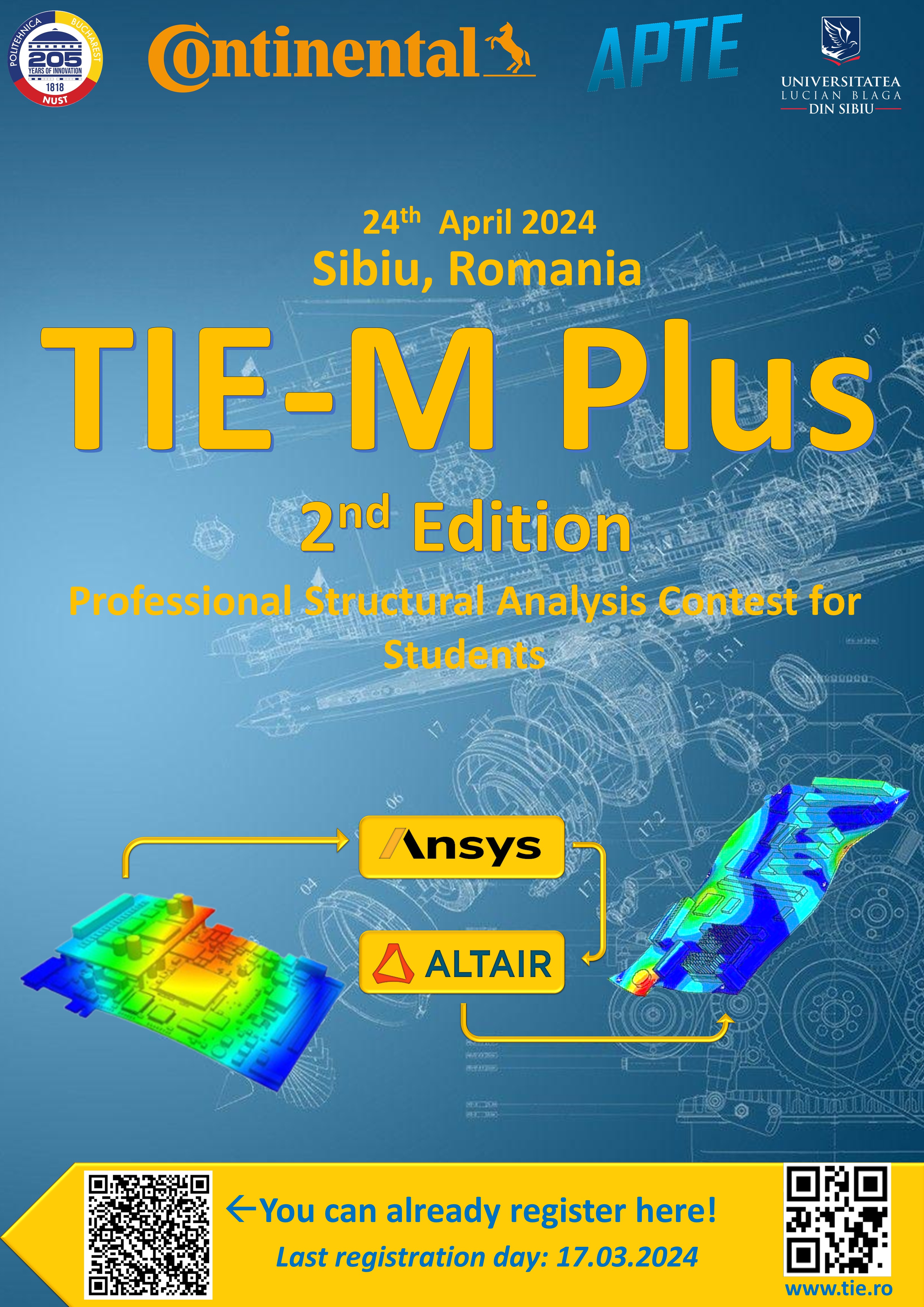

TIE_M Plus 2024 Third Edition Promotional Poster & Registration LINK